#### Bachelor's Thesis

## Quality Control of Modules in the ATLAS Inner Tracker

## Qualitätskontrolle von Modulen im ATLAS 'Inner Tracker'

prepared by

Leander Teich

from Göttingen

at the II. Physikalischen Institut

Thesis number: II.Physik-UniGö-BSc-2025-02

Thesis period: 9th April 2025 until 16th July 2025

First referee: Prof. Dr. Arnulf Quadt

Second referee: Priv. Doz. Dr. Markus Keil

#### **Abstrakt**

Diese Arbeit untersucht die Durchführbarkeit und Leistungsfähigkeit der Parallelisierung der elektrischen Qualitätssicherungstests (QS-Tests) von RD53B Modulen, mit besonderem Fokus auf die Tests im Rahmen des YARR-Software-Framework's. Erste Tests zeigten vielversprechende Ergebnisse. Anschliessende Arbeiten am Aufbau erweiterten die Kapazität für gleichzeitige Tests von zwei auf vier Module. Die Analyse umfasste verschiedene elektrische Charakterisierungstests, insbesondere die IV-Messungen, die aufgrund dedizierter Hochspannungsquellen ein erhebliches Parallelisierungspotenzial aufwiesen. Die übrigen elektrischen QC-Tests hingegen sind, aufgrund der zugrunde liegenden Softwarearchitektur sowie des Einzelinstanz-Betriebsmodells von YARR, lediglich sequentiell durchführbar. Darüber hinaus wurde eine systematische Bewertung der Parallelisierbarkeit der auf YARR basierenden Funktionstests durchgeführt, wobei die Ausführungseffizienz verschiedener Scan-Typen betrachtet wurde. Die Ergebnisse zeigten, dass bestimmte Scan-Routinen wie MHT, TUN und PFA zwar von einer parallelen Ausführung profitieren können, die erzielten Zeiteinsparungen jedoch nicht ausreichten, um eine vollständige Parallelisierung aller Module zu rechtfertigen, da dies einen synchronen Fortschritt in allen weiteren Prozessphasen vorher und nachher erfordert hätte. Diese Arbeit zeigt, dass zwar bestimmte Tests effektiv parallelisiert werden können, jedoch grundlegende Änderungen an der bestehenden Software notwendig wären, um eine vollständige Parallelisierung aller Tests - insbesondere der elektrischen Charakterisierung - zu ermöglichen.

Stichwörter: Physik, Bachelorarbeit, YARR, ITk, ATLAS Experiment, Pixel Detektor

#### Abstract

This thesis investigates the feasibility and performance of parallelizing the electrical quality control (QC) tests of RD53B modules, with a focus on the testing within the YARR software framework. Initial tests demonstrated the potential for parallel execution, prompting subsequent upgrades that expanded the capacity for simultaneous testing from two to four modules. The analysis included various electrical characterisation tests, notably the IV measurements, which indicated a significant degree of parallelisation potential, owing to dedicated high-voltage power supplies. Conversely, the remaining electrical QC tests were determined to be inherently sequential in nature, primarily due to the software architecture and the single-instance operational model of YARR. Furthermore, a systematic evaluation of the parallelizability of YARR based functionality tests was performed, looking at the execution efficiencies of different scan types. The results revealed that while the MHT, TUN, and PFA scan routines could benefit from parallel execution, the overall time savings did not justify running all modules simultaneously, as it required synchronised progress throughout all testing stages. This work highlights that while certain tests can be effectively parallelised, major revisions to existing software would be necessary to enable parallelisation of all tests - specifically the electrical characterisations.

Keywords: Physics, Bachelor thesis, YARR, ITk, ATLAS experiment, Pixel Detector

## Contents

| 1.        | Intr | oducti  | ion                            | 1      |

|-----------|------|---------|--------------------------------|--------|

| 2.        | The  | Stand   | dard Model of Particle Physics | 3      |

|           | 2.1. | Bosons  | ıs                             | <br>3  |

|           | 2.2. | Fermi   | ions                           | 4      |

| 3.        | Det  | ectors  |                                | 7      |

|           | 3.1. | The L   | LHC                            | 7      |

|           | 3.2. | The A   | ATLAS Experiment               | 7      |

|           | 3.3. | The B   | Bethe-Bloch Formula            | 8      |

|           | 3.4. | Gaseo   | ous detectors                  | 10     |

|           | 3.5. | Semico  | conductor detectors            | 10     |

|           | 3.6. | Tracki  | ing & Vertexing                | 13     |

|           | 3.7. | Calori  | imeters                        | 13     |

| 4.        | The  | ITk U   | $\operatorname{Upgrade}$       | 15     |

|           | 4.1. | Genera  | ral Structure                  | <br>15 |

|           | 4.2. | ITkPi   | ix Quad Modules                | 17     |

| <b>5.</b> | Mod  | dule Q  | Quality Control (QC)           | 19     |

|           | 5.1. | QC Pı   | rocess Overview                | <br>19 |

|           | 5.2. | Electri | rical QC Tests & Procedure     | <br>20 |

|           |      | 5.2.1.  | Electrical Characterisation    | <br>21 |

|           |      | 5.2.2.  | YARR Scans                     | 25     |

| 6.        | Test | Setup   | p                              | 29     |

|           | 6.1. | Hardw   | ware                           | <br>29 |

|           |      | 6.1.1.  | Climate Chamber                | <br>30 |

|           |      | 6.1.2.  | Sensors & Labremote            | <br>30 |

|           |      | 6.1.3.  | Database and Grafana           | <br>31 |

|           |      | 6.1.4   | Interlock Systems              | 32     |

#### Contents

|          |                     | 6.1.5.                                                  | Mounting Plate                            | 32                                            |

|----------|---------------------|---------------------------------------------------------|-------------------------------------------|-----------------------------------------------|

|          | 6.2.                | Softwa                                                  | re                                        | 34                                            |

|          |                     | 6.2.1.                                                  | Module QC Tools                           | 34                                            |

|          |                     | 6.2.2.                                                  | YARR                                      | 34                                            |

| 7.       | Feas                | sibility                                                | and Performance of Parallelised Module QC | 37                                            |

|          | 7.1.                | Electri                                                 | cal Characterisation                      | 37                                            |

|          |                     | 7.1.1.                                                  | IV Measurement                            | 38                                            |

|          |                     | 7.1.2.                                                  | Further Electrical QC Tests               | 40                                            |

|          | 7.2.                | YARR                                                    | -Based Functional Scans                   | 41                                            |

|          |                     | 7.2.1.                                                  | Initial Tests and Software Verification   | 41                                            |

|          |                     | 7.2.2.                                                  | Scan Runtime                              | 42                                            |

|          |                     | 7.2.3.                                                  | Front-End-Wise Scan Times                 | 44                                            |

|          |                     | 7.2.4.                                                  | Scan Routines                             | 46                                            |

|          |                     |                                                         |                                           |                                               |

| 8.       | Disc                | cussion                                                 |                                           | 49                                            |

| 8.       | <b>Disc</b> 8.1.    |                                                         | cal Characterisation                      | <b>49</b> 49                                  |

| 8.       |                     | Electri                                                 |                                           |                                               |

| 8.       |                     | Electri                                                 | cal Characterisation                      | 49                                            |

| 8.       |                     | Electri<br>8.1.1.                                       | cal Characterisation                      | 49<br>49                                      |

| 8.       | 8.1.                | Electri<br>8.1.1.<br>8.1.2.<br>YARR                     | cal Characterisation                      | 49<br>49<br>50                                |

| 8.       | 8.1.                | Electri<br>8.1.1.<br>8.1.2.<br>YARR<br>8.2.1.           | cal Characterisation                      | 49<br>49<br>50<br>50                          |

|          | 8.1.<br>8.2.        | Electri<br>8.1.1.<br>8.1.2.<br>YARR<br>8.2.1.           | cal Characterisation                      | 49<br>49<br>50<br>50<br>50                    |

| 9.       | 8.1.<br>8.2.        | Electri<br>8.1.1.<br>8.1.2.<br>YARR<br>8.2.1.<br>8.2.2. | cal Characterisation                      | 49<br>49<br>50<br>50<br>50<br>51              |

| 9.<br>10 | 8.1.<br>8.2.<br>Con | Electri<br>8.1.1.<br>8.1.2.<br>YARR<br>8.2.1.<br>8.2.2. | cal Characterisation                      | 49<br>49<br>50<br>50<br>50<br>51<br><b>55</b> |

## 1. Introduction

The LHC's upcoming upgrade to the High-Luminosity (HL-) LHC will significantly enhance its capabilities with a planned instantaneous luminosity of  $7.5 \cdot 10^{-34} \, \mathrm{cm^{-2} \, s^{-1}}$  and a planned center of mass energy  $\sqrt{s} = 14 \, \mathrm{TeV}$  [1]. This promises increased statistical precision and more frequent observation of rare phenomena at even higher energies than before, possibly opening the door to newly discovered physics. The upgrade however also poses significant challenges for the experiments and detectors such as ATLAS due to the ever increased data rate and radiation exposure among others. To mitigate this, the ATLAS inner detector is being replaced by an all-silicon Inner Tracker (ITk), designed to withstand the increased radiation levels and data rates for the upcoming run. The sensor modules at the heart of the upgrade are crucial to the continued operation of the ATLAS detector which is why they have to be characterised and tested meticulously beforehand and stringent standards for quality control be set in place as to prevent premature sensor failures as the hardware can not be replaced during operation [2].

This thesis will focus on precisely these quality control tests at an attempt to automate these processes in order to adequately process the  $\approx 1800$  modules assigned to the German ITk-Pixel cluster for testing [3]. The feasibility and degree of parallelisation of these quality control tests is to be assessed as part of an overall effort to streamline and optimize the quality control process for a higher throughput.

# 2. The Standard Model of Particle Physics

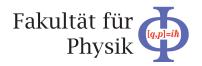

The Standard Model of particle physics (hereafter: SM) represents the most comprehensive theoretical framework for elucidating the fundamental principles that govern the universe, and by extension, life itself. This model offers a detailed account of the elementary particles that constitute matter and the forces through which they interact, with the notable exception of gravity among others. The SM is not only a cornerstone of contemporary physics but also a testament to humanity's enduring quest to comprehend the deepest workings of nature. The Standard Model categorises particles into two primary classes: bosons and fermions, distinguished by their intrinsic spin and represented in Figure 2.1 [4].

#### 2.1. Bosons

Bosons are force-carrying particles characterised by an integer spin (S = 0 or S = 1). These particles mediate the fundamental forces that govern interactions between matter particles [4]. The SM encompasses three types of gauge bosons and one scalar boson, each associated with a specific quantum field theory:

- Photon ( $\gamma$ ): The mediator of the electromagnetic force, responsible for electromagnetic interactions, commonly observed in phenomena such as chemical bonding and light emission. This force acts between charged particles, with photons being charge-neutral. It is described by Quantum Electrodynamics (QED).

- W and Z Bosons ( $W^{\pm}$ , Z): Mediators of the weak nuclear force, crucial in processes such as radioactive decay and matter-antimatter asymmetry. They are described by Quantum Flavourdynamics (QFD) [6].

- Gluon (g): The mediator of the strong nuclear force, binding quarks within protons and neutrons through a threefold colour charge. It is described by Quantum

Figure 2.1.: Illustration of the known particles comprising the Standard Model. Illustra-

Chromodynamics (QCD) and explains phenomena such as confinement, whereby single quarks cannot be observed independently, necessitating a bound state of at least two quarks [7–9].

• **Higgs Boson** (*H*): An excitation in the Higgs field. The corresponding Higgs mechanism, which endows elementary particles with mass through their interaction with the Higgs field (*H*), is a crucial component of the SM, providing masses to the W and Z bosons as recently discovered by CMs and ATLAS [10, 11].

#### 2.2. Fermions

tion from [5].

Fermions are matter particles characterised by a half-integer spin  $(S = \frac{1}{2})$ . They include leptons and quarks, which can be further subdivided into three generations. The SM comprises six types of quarks, organised into three generations. Each generation consists

of an up-type quark with a charge of  $+\frac{2}{3}$  and a down-type quark with a charge of  $-\frac{1}{3}$  [4]. The mass of quarks increases progressively across generations [12]. Bound states of quarks (hadrons) can be further classified based on the total spin of the bound state, with baryons having a half-integer spin and mesons having an integer spin.

Similarly, the six leptons are divided into three generations, each comprising a charged particle and its neutral neutrino counterpart. Charged leptons carry a weak isospin of  $-\frac{1}{2}$ , while their neutral counterparts (neutrinos) have a weak isospin of  $\frac{1}{2}$ . The masses of charged leptons increase with each generation, whereas neutrinos, once considered massless, are now understood to possess very small but non-zero masses [12].

The intricate mathematical formalism underlying the description of interaction processes involving two or more of the aforementioned particles can be represented visually using Feynman diagrams. These diagrams serve as a shorthand for calculating the matrix elements that determine the probability amplitudes of particle interactions. Ultimately, these theoretical predictions can be implemented in Monte Carlo simulations and compared with experimentally measured cross sections to test the validity of the Standard Model and similar models.

### 3. Detectors

Detectors are at the heart of every high energy particle physics experiment. They are what physicists see the interesting microcosm of fundamental interactions through. Generally a detector is used to track and or identify specific particles within a collision experiment. Hereby only being able to detect the collision products, out of which the actual collision partners can be reconstructed. The sheer variety of particles and observables requires a set of different detector types with varying goals and measurement paradigms.

#### 3.1. The LHC

Testing the predictions of the SM and peering deeper into the fundamental principles of the universe than ever before, the Large Hadron Collider (LHC) allows for groundbreaking discoveries at energies never seen before. Located at CERN (the European Centre for Nuclear Research) near Geneva, Switzerland, the LHC is an approximately 26.7km circumference circular particle accelerator colliding beams of protons and heavy ions at a centre of mass energy up to  $\sqrt{s} = 14 \,\text{TeV}$  [13, 14]. A multitude of experiments are set up around these collision points including ATLAS, CMS, LHCb and ALICE, the focus of this project being the ATLAS Detector.

#### 3.2. The ATLAS Experiment

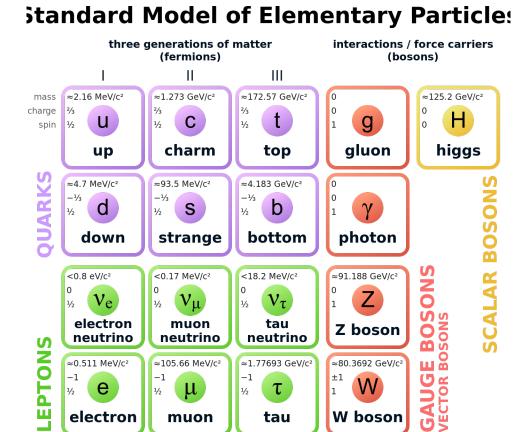

The ATLAS (A Toroidal LHC ApparatuS) detector is one of the experiments set up at the LHC to research elementary particles and their interactions as to further our understanding of the universe, such as was the case in July 2012 when it, along with the CMS collaboration, claimed the discovery of the Higgs boson [10, 11]. It is constructed in a discrete layered, onion like fashion with different detector shells responsible for identifying different key aspects of the collision products, as illustrated in Figure 4.1 making it a general purpose detector [15]. The Inner Detector with unique tracking capabilities is followed by an electromagnetic and a hadronic calorimeter to determine energy scales as well as a final outermost muon detector to measure their respective energies.

#### 3. Detectors

Figure 3.1.: Schematic cross-section of the ATLAS detector, illustrating its layered structure and typical penetration depths of different particles. Image by the ATLAS Collaboration [16].

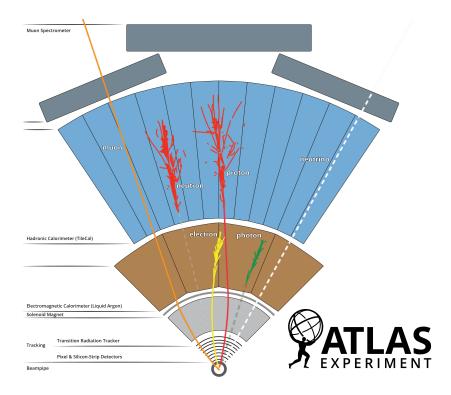

Most notable and eponymous are the magnets built into the detector setup. The ATLAS detector utilizes two distinct magnets to alter the path of charged collision products in order to calculate the respective energies. One being a Solenoid magnet surrounding the inner detector core reaching field strengths of up to 2 T causing trajectories of charged particles to bend in the cross sectional plane, orthogonally to the particle beam [17]. The outer most magnet being composed of a central barrel toroid and two end cap toroids provide a field strength of up to 3.9 T allowing for measurement of momenta of muons [17]. The magnet system is illustrated in Figure 3.2.

#### 3.3. The Bethe-Bloch Formula

The Bethe-Bloch Formula (sometimes also referred to as just the Bethe Formula) describes the mean energy loss per distance travelled of a specified charged particle in the presence of matter [19, 20]. The formula and its associated functional dependencies are of significant interest in the field of particle physics, as the detectors commonly used in such experiments rely on the precise measurement of energy loss to identify and characterise particles.

Figure 3.2.: Schematic outline of the two main magnet systems embedded into the detector. Image by the ATLAS Collaboration [18].

$$\left\langle -\frac{dE}{dx} \right\rangle = \frac{4\pi}{m_e c^2} \cdot \frac{z^2}{\beta^2} \cdot \left(\frac{e^2}{4\pi\varepsilon_0}\right)^2 \cdot n \cdot \left[ \ln \frac{2m_e c^2 \beta^2 \gamma^2}{I} - \beta^2 - \frac{\delta(\beta\gamma)}{2} \right]$$

(3.1)

The formula 3.1 accounts for various factors, including the charge z (in units of the elementary charge) and velocity  $\beta$  (in units of the speed of light) of the particle, the electron density of the material  $n = \frac{N_A \cdot Z \cdot \rho}{M_m \cdot A}$  (taking into account the atomic number Z, mass number A, the molar mass  $M_m$  and density  $\rho$ ), and the mean excitation potential I (in eV), which collectively influence the rate of energy loss. Different parts of the curve can be attributed to different phenomena causing the energy loss, including but not limited to bremsstrahlung and ionisation. For high energies (above  $\approx 10 \,\mathrm{MeV}$ ) the energy-loss can predominantly be attributed to bremsstrahlung and resulting  $e^+$   $e^-$  pair production of photons.

The radiation length is a crucial parameter in the study of electromagnetic interactions in matter, particularly in high-energy physics experiments like those conducted at the LHC. It represents the mean distance over which a high-energy electron loses all but  $\frac{1}{e}$  of its energy with Euler's constant  $e \approx 2.72$ . Thus this characteristic length imposes boundaries on the minimum size of a given calorimeter. Bremsstrahlung and ionisation are the primary mechanisms of energy loss for charged particles traversing matter. While ionisation dominates at lower energies, bremsstrahlung becomes significant at higher energies, especially for electrons and positrons. The critical energy,  $E_c$ , is the energy at which the energy loss due to bremsstrahlung equals that due to ionisation. This energy is material-dependent and is a key factor in the design and operation of detectors.

#### 3. Detectors

In the context of the ATLAS detector at the LHC, understanding these processes is essential for accurate particle identification and energy measurement. The ATLAS detector uses a combination of calorimeters and tracking systems to measure the energy and momentum of particles. The calorimeters are designed to absorb and measure the energy of particles, relying on the principles of bremsstrahlung and ionisation to do so. The radiation length is particularly relevant in the design of electromagnetic calorimeters, which are optimised to measure the energy of electrons and photons by exploiting these energy loss mechanisms.

#### 3.4. Gaseous detectors

Gaseous detectors rely on passing particles ionizing the gas within the detector volume. Through a voltage applied between the cathode and anode, the resulting electric field causes the ionised gas atoms and electrons to drift towards the respective electrode where they can be detected as an electrical signal. Depending on the voltage between the electrodes the detector can operate in different modes with a higher voltage leading to increased ionisation and thus amplifying the signals through a larger gas-amplification factor however also increasing the dead time of the detector in the process [21].

#### 3.5. Semiconductor detectors

Semiconductor based detectors such as found in the Inner tracker of the ATLAS Experiment allow for high precision trajectory reconstruction thus allowing more precise measurements of the subatomic world. The following thesis project will be mostly concerned with precisely this type of detector.

An electron within a single atom can occupy discrete energy levels as well described by quantum mechanics. When considering the energy of two or more overlapping atomic orbitals, these discrete energy levels can reshape, split and slightly shift. As a consequence of a periodic crystalline structures, the formation of high energy-level-density bands can be observed. These near to continuous regions of closely packed energy levels are referred to as an energy band. A band gap in this case refers to the absence of such regions, indicating no electrons with that energy within the observed crystal structure [22]. Generally a band can be classified as a conduction or a valence band depending on whether it lies above or below the Fermi energy, respectively. The electrical conductivity of a material is strictly dependent on the electrons in the conduction band and thus by extension also the ability of the electrons to be lifted from the valence band into the conduction band by means of

excitation (such as thermal excitation).

Materials with a partially filled conduction band (the Fermi energy lies within the conduction band) are known as conductors or metals. If the valence and conduction band are separated by a bandgap (the Fermi energy lies within the bandgap) the electrical characteristics are that of an insulator or semiconductor, depending on the energy of the bandgap. For bandgaps above  $\approx 5\,\mathrm{eV}$  materials are typically categorised as insulators due to the high energy required to excite the electrons from the valence band into the conduction band and thus allow for electrical conductivity [22]. Semiconductors are characterised by lower energy bandgaps, leading to a conductivity dependent on the energy of the electrons in the material and thus susceptible to external thermal excitation or even photoabsorption. Silicon is a common choice of semiconductor and also used in the Atlas detector.

To further alter the electrical characteristics of a semiconductor, it can be doped. This refers to the process of introducing impurities into the crystal lattice by means of accelerating ions of other materials into the semiconductor [22]. Through a well controled heating and cooling cycle, movement at the atomic scale is introduced, allowing for the lattice structure to re-order itself and thus incorporate the doped ions. This process is known as annealing.

Generally two types of doping can be differentiated, n-Type and p-Type based on the number of valence electrons of the dopant.

- **n-type**: The dopants have more valence electrons than the base semiconductor. This leads to an excess of negative charges in the doped area.

- **p-type**: The dopants have fewer valence electrons than the base semiconductor. These electron holes result in an effective positive charge region.

Joining both p-type and n-type doped semiconductors gives rise to a fundamental building block of modern electronics, an n-p junction. Its working principle is rooted in the interaction between the two regions when they are brought into contact. At the interface of the n-type and p-type materials, electrons from the n-type region diffuse into the p-type region and recombine with holes. Equivalently, holes from the p-type region diffuse into the n-type region and recombine with electrons. This movement of charge carriers results in the formation of a depletion region, a zone around the contact area where there are no free charge carriers. The depletion region acts as an insulating barrier preventing further movement of charge carriers.

As electrons and holes recombine, they leave behind charged ions (positive ions in the n-type region and negative ions in the p-type region). This separation of charges creates

#### 3. Detectors

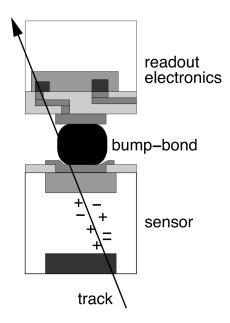

Figure 3.3.: Schematic of a single-pixel semiconductor based detector. The electron & hole pairs will, similar to as mentioned in the gaseous detectors, cause a signal in the electrode near the bump-bond through the drifting charges. Used from [23].

an electric field across the depletion region. The built-in electric field opposes further diffusion of charge carriers, establishing an equilibrium. When an external voltage is applied such that the p-type is connected to the positive terminal and the n-type to the negative terminal, the potential barrier of the depletion region is reduced. This allows charge carriers to flow across the junction, resulting in current flow. Electrons move from the n-type to the p-type region, and holes move in the opposite direction, allowing the device to conduct electricity. This is known as the forward Bias. When applying the voltage in the opposite polarity, the depletion region increases in size, even further preventing current flow across the junction. This is known as the reverse Bias [22]. Semiconductor Detectors are comprised of many individual pixels, each being an n-p junction. A passing high energy particle can excite several valence electrons inside the detector material (see 3.3) and thus create an electron-hole pair. Through the electric field across the junction, both start drifting towards opposite ends of the junction, inducing a current in the readout electronics and thus a measurable signal as illustrated in Figure 3.3.

A passing particle may also interact not by ionisation but by non-ionizing energy loss (NIEL) processes, imparting energy into the lattice structure in the form of phonons. With enough energy this can cause permanent atomic dislocation from the regular crystal structure and potentially even the removal of individual atoms from the material, introducing defects into the structure and altering the dopant concentration completely changing electrical characteristics [24]. This radiation based damage is especially detrimental to the ATLAS Inner Tracker system due to its highly intricate and microscopic

feature design as well as the spatial proximity to the beam pipe and thus large amounts of radiation.

#### 3.6. Tracking & Vertexing

Given the data gathered by aforementioned detector types, two key techniques to further process and more easily apply to the underlying particle collision experiment are particle tracking and vertexing. Tracking is the process of determining the path taken by a detected particle as it passes through the detector system. In the presence of a magnetic field, the momentum of such charged particles can be determined, further aiding in the identification of collision products [21]. In gaseous detectors, such as drift chambers and any variation of such detector, charged particles ionize the surrounding gas, creating an ion - electron trail. Such a trail can subsequently be picked up by the nearest electrodes allowing for the measurement of a spatially resolved trajectory. Using the constant drift velocity of a particle, a trajectory can even be fully reconstructed based on the temporal segmentation of the signal such as in a time projection chamber. Semiconductor detectors have an inherently high spatial resolution, allowing for multiple layers of detectors to precisely track individual particles. Vertexing is the process of identifying the position in space where a given particle originates from, namely to reconstruct the last interaction vertex [21]. This is particularly important for studying short-lived particles which do not make it to a detector within their respective decay-length and reconstructing intermediate particle processes.

#### 3.7. Calorimeters

Calorimeters are devices used to measure the energy of passing particles, making up the outer thicker layers of the ATLAS detector [15]. They operate on the principle of absorbing the entire energy of a particle and converting it into a measurable signal, typically through a cascade of interactions. When a high-energy particle enters the calorimeter, it undergoes a series of interactions, such as ionisation and bremsstrahlung, leading to the production of further particles as can be described using the Bethe-Bloch Formula (see 3.3). These particles again interact with the material, creating a shower of particles. The calorimeter is designed to absorb this shower, converting the energy into light (in scintillators) or charge (in ionisation detectors), which is then collected and measured [25]. The total signal is proportional to the energy of the original particle, allowing for precise particle energy reconstruction as per the Shockley-Ramo-theorem [26, 27]. Calorimeters are

#### 3. Detectors

typically divided into electromagnetic and hadronic types, optimised for measuring electrons/photons and hadrons, respectively. Generally, hadronic showers are more complex and significantly longer due to the large plethora of particles and interaction mechanisms as well as being able to contain itself an electromagnetic shower within.

## 4. The ITk Upgrade

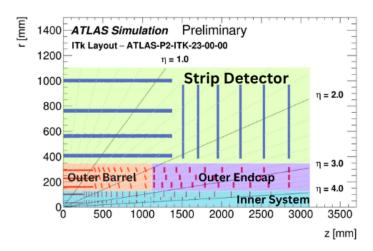

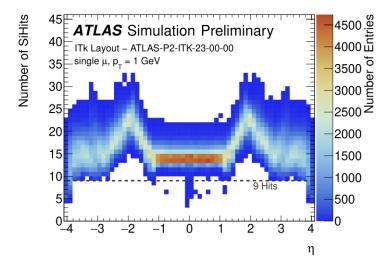

As part of the Phase II upgrade during the third long shutdown of the LHC (LS3), scheduled for 2026-2028, the ATLAS tracking detector will transition from the current Inner Detector (ID) system to a new all-silicon Inner Tracker (ITk) system. This upgrade is necessary to accommodate the projected increases in luminosity, pile-up, and radiation levels, as well as to replace degraded sensors. The ITk system will offer tracking coverage up to a pseudorapidity of  $|\eta| \le 4$  and will utilise, among others, pixels with a  $50 \,\mu\text{m} \times 50 \,\mu\text{m}$  footprint, covering a total combined area of approximately  $13 \,\text{m}^2$  [2].

#### 4.1. General Structure

The full structure of the ITk will consist of approximately 9164 modules [28] arranged in a nested barrel geometry, complemented by a series of endcap disks [29], ensuring complete coverage up to  $|\eta| = 4$ . A cross-sectional view of the planned module arrangement is presented in Figure 4.1.

The barrel section of the ITk comprises five cylindrical layers of pixel modules. These modules are mounted on lightweight mechanical support structures known as staves, which are, in turn, attached to longitudinal carbon-fiber-reinforced elements that form the structural spine of the barrel. This design guarantees mechanical stability under thermal and mechanical stress. Each stave houses multiple quad modules mounted on both sides to maximise spatial efficiency.

A key feature of the ITk design is its inclined geometry in the barrel section. Unlike the flat orientation of sensors in the current Pixel Detector, the modules in the ITk barrel are tilted with respect to the beam axis, particularly in the outer layers. This design enhancement improves coverage, especially for tracks at higher pseudorapidity. The inclination increases the effective path length of traversing particles within the sensor, thereby enhancing hit efficiency and spatial resolution for shallow-angle tracks [2].

The endcap region consists of a series of concentric disks, each populated with pixel modules mounted on wedge-shaped support structures known as petals. This arrangement ensures hermetic tracking coverage in the forward region, where track density is highest

#### 4. The ITk Upgrade

Figure 4.1.: A cross-sectional view of the updated ITk layout. Only one quadrant is shown. Based on [28].

due to the boosted topology of LHC collisions.

The ITk Strip Detector, by contrast, features larger-area modules and longer sensor strips optimised for tracking in lower-occupancy regions, with separate barrel and endcap layouts tailored for coarse-grained but efficient reconstruction.

The number of pixel hits per track is highly dependent on the track's pseudorapidity  $\eta$ . As illustrated in Figure 4.2, the inclined layout and denser layering in the forward region help maintain high hit multiplicity even for tracks with  $2.5 < |\eta|$ . This capability is essential for preserving the ITk's excellent pattern recognition and track reconstruction performance in the high-pile-up environment anticipated during the HL-LHC era.

Figure 4.2.: Expected hit coverage of the updated ITk layout for varying pseudorapidities given a single muon sample event. Source: [28]

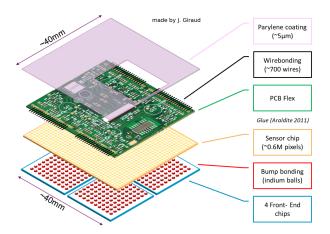

#### 4.2. ITkPix Quad Modules

The pixel modules in the ITk system are based on radiation-tolerant silicon sensor technologies and are optimised for high spatial resolution and fast readout to handle the dense hit environment of the HL-LHC. They are specifically designed for the expected occupancy and radiation levels of their respective detector regions, with pixel pitch and readout granularity adapted as needed. The modules primarily utilise n-in-p type silicon detectors, featuring  $384 \times 400$  individual pixels per front-end chip, resulting in an effective resolution of approximately 1.3 Gpx. The hybrid pixel detector modules consist of a single monolithic silicon sensor that is bump-bonded to four individual RD53 front-end (FE) chips. The FE chips are arranged in a  $2 \times 2$  configuration and are responsible for analog signal amplification, digitisation, and zero suppression [30]. The sensor and FE chips together form the bare module, which is glued to the back side of a flexible printed circuit board (flex PCB). Electrical connections between the flex and the front-ends are established using  $25 \,\mu$ m diameter wire bonds that extend along the module's entire edge. The flex PCB houses two connectors for power and data readout, as well as passive components such as decoupling capacitors to ensure signal integrity.

Figure 4.3.: Annotated schematic of the different layers composing a single quad module. Missing in this representation are the canopies (present only on outer barrel modules), attached onto the PCB flex to shield wire bonds below. Source: [31]

The chipset discussed in this thesis is the RD53B (also known as ITkPixV1.1), which represents the second generation of the RD53 family. The RD53A serves as a half-scale demonstrator developed to test various designs and architectures, acting as an R&D prototype. The RD53B provides a full-scale backbone for further testing and verification with experiment-specific front-ends (ATLAS and CMS). The RD53C (also known as ITkPixV2) is the final production version that incorporates many hardware fixes from the previous

#### 4. The ITk Upgrade

generation [32].

During production and testing, the quad modules are placed onto a mechanical carrier to ensure mechanical stability throughout assembly, operation, and shipment.

In the final assembly phase, the modules are mounted to carbon-composite-based load structures referred to as Loaded Local Supports (LLS), which also feature a thermal connection to a cooling system [33]. Along these LLSs, modules are connected in serial power chains to minimise cabling, since such a configuration necessitates only one current source per serial chain.

## 5. Module Quality Control (QC)

As there is no viable method to service modules once integrated into the final ITk system, their functionality must be verified before assembly to ensure a usable and functional lifespan of at least 10 years. The Module Quality Control tests comprise a series of analyses and procedures performed on every module to determine whether it functions within acceptable limits. This allows for the identification and exclusion of malfunctioning modules prior to integration into the final build. The fraction of modules certified for use out of the total production volume is known as the yield, which in turn defines the required overproduction needed to reach the target of approximately 8372 modules for the ITk pixel subsystem [34]. The QC process described here reflects the procedure at the time of writing this thesis. It may not be final, as, despite the project transitioning from pre-production to production, ongoing improvements and refinements to the QC workflow continue to be proposed and implemented.

#### 5.1. QC Process Overview

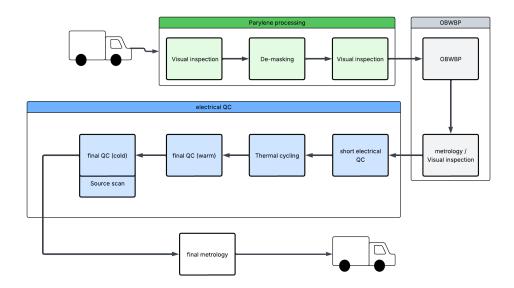

The local processing workflow for modules received in Göttingen is illustrated in Figure 5.1. Upon arrival, each module undergoes an initial visual inspection to identify any signs of damage incurred during transport or earlier manufacturing steps. After coating, the parylene de-masking process exposes the electrical contact pads, pickup points, and the full backside of the module for further testing. Parylene masks are applied beforehand to protect the board and to prevent coating of electrically active or contact-critical areas.

Subsequently, the Outer Barrel Wire Bond Protection (OBWBP) is installed. This involves gluing protective canopies onto the printed circuit board (PCB) to shield the delicate wire bonds on the sides from mechanical damage during handling and operation. After OBWBP installation, a second visual inspection is performed to verify correct placement and adhesion, followed by a metrological assessment.

Once these preparatory steps are complete, the module enters the electrical QC stage. This begins with a basic functional test to check for short circuits or obvious electrical defects. To assess robustness against thermal stress-expected during ITk operation, the

#### 5. Module Quality Control (QC)

module is subjected to a series of thermal cycles, simulating repeated transitions between +40 °C and -45 °C.

Following thermal cycling, the module undergoes a final series of QC measurements. These include a warm electrical QC test at room temperature to validate basic functionality and a cold electrical QC test at the operational temperature of  $-15\,^{\circ}$ C, during which a source scan is performed to assess the module's response to incident radiation. The entire QC process concludes with final metrology to ensure that flatness has been achieved, enabling proper integration into the designed truss structure. These measurements are critical for ensuring the long-term reliability and performance of modules in the ITk detector environment.

Figure 5.1.: Flowchart overview of the module processing in Göttingen. Excluding the last metrology step, the entire process can be segmented into a parylene processing step, an Outer Barrel Wire Bond Protection (OBWBP) step, and an electrical QC procedure. The order of operations for the electrical QC and final metrology can be arbitrarily swapped.

#### 5.2. Electrical QC Tests & Procedure

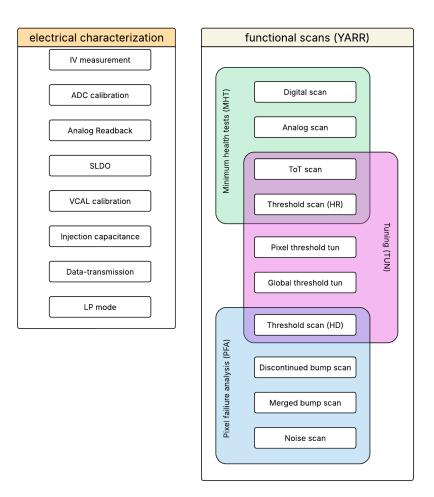

The electrical QC tests can broadly be categorised into two groups:

- 1. Electrical characterisation measurements verifying key metrics and electrical behaviour.

- 2. Functional scans using YARR (further detailed in section 6.2.2) to evaluate data-taking capabilities via diagnostic scans, calibrations, and tunings.

A schematic overview is provided in Figure 5.2.

Figure 5.2.: Overview of electrical characterisation measurements (left) and YARR-based functionality scans (right) executed during a single electrical QC run. The three base routines - MHT (minimum health test), TUN (tuning), and PFA (pixel failure analysis) each share some scans with one another. Typical execution order is moving from top to bottom.

#### 5.2.1. Electrical Characterisation

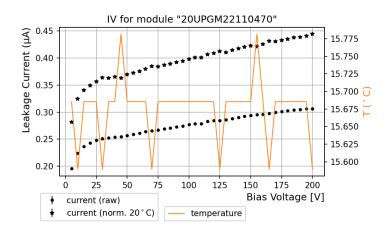

IV Measurement The IV measurement characterises the current drawn as a function of the high-voltage (HV) bias. During an IV scan, the module's HV supply is ramped from 0 V to 200 V in 5 V steps, while the current is continuously measured shortly after stabilising at each voltage level. One of the main goals of the IV measurement is to detect damage to the module, which can manifest as an early breakdown or excessively high leakage current. A sample test output is given in Figure 5.3.

#### 5. Module Quality Control (QC)

Figure 5.3.: Sample IV characterisation for module Q51 based on standard processing tools output.

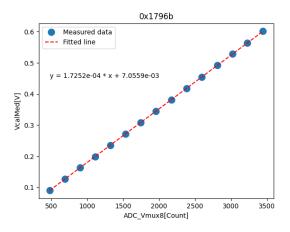

ADC Calibration The ADC calibration verifies the accuracy of the internal analogue-to-digital (ADC) converters used to measure on-chip voltages and currents. This is done by applying a known voltage (typically via scanning the internal  $V_{cal}$  DAC) and comparing the ADC output to an external multimeter measurement. A linear fit extracts the ADC slope and offset, which are compared to acceptance criteria. This calibration is critical for all subsequent measurements relying on ADC readout and is stored in the chip configuration files.

Figure 5.4.: Sample output of the ADC calibration of one FE as part of module Q49.

Analogue Read-back The analogue read-back test confirms the correct operation of internal voltage and current monitoring circuits. Using the calibrated ADC, various  $V_{MUX}$  and  $I_{MUX}$  values are read out to determine internal supply voltages (e.g.,  $V_{DDA}$ ,  $V_{DDD}$ ),

| Parameter                 | Analysis result | QC criteria    | Pass |

|---------------------------|-----------------|----------------|------|

| ADC CALIBRATION SLOPE     | 0.173           | [0.15, 0.224]  | True |

| ADC CALIBRATION OFFSET    | 7.0             | [-9, 31]       | True |

| ADC CALIBRATION LINEARITY | 0.3             | [0.0, 4.0]     | True |

| ADC ANAGND30 MEAN         | 0.018           | [0.012, 0.023] | True |

| ADC ANAGND30 STD          | 0.0             | -              | -    |

Table 5.1.: Summary of ADC calibration results of FE 0x1796b (part of module Q49).

reference voltages (e.g.,  $V_{refA}$ ,  $V_{refD}$ ), and currents (e.g., input and shunt currents). Temperature sensors are also read out and validated. All measured values are compared to expected ranges to detect possible configuration or regulation issues.

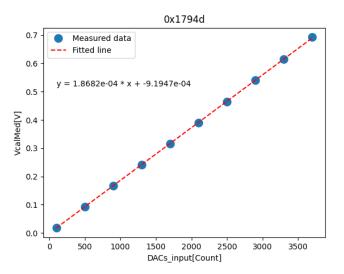

$V_{cal}$  Calibration This test characterises the internal DAC responsible for charge injection ( $V_{cal}$ ). A scan over the DAC range is performed while monitoring the output voltage with an external multimeter. Slope, offset, and linearity are extracted and compared to expectations. Both small and large range settings are tested. Accurate  $V_{cal}$  calibration is essential for threshold tuning and charge injection. A sample output is presented in Figure 5.5 and Table 5.2.

Figure 5.5.: Measurements of the  $V_{cal}$  calibration procedure with the measured voltage as a function of the specific DAC input value for a single FE of the module Q49 in the medium DAC range.

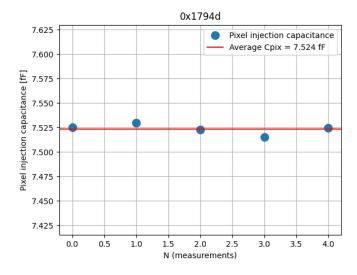

**Injection Capacitance** This test measures the on-chip injection capacitor, which, combined with the  $V_{cal}$  DAC, defines the injected charge during calibration pulses. The

#### 5. Module Quality Control (QC)

| Parameter                              | Analysis result | QC criteria  | Pass |

|----------------------------------------|-----------------|--------------|------|

| $V_{cal}$ MED SLOPE                    | 0.19            | [0.16, 0.24] | True |

| $V_{cal}$ MED OFFSET                   | -1.0            | [-23, 17]    | True |

| $V_{cal}$ MED LINEARITY                | 1.03            | [0.0, 4.0]   | True |

| $V_{cal}$ MED LINEARITY SMALL RANGE    | 0.57            | -            | -    |

| $V_{cal}$ HIGH SLOPE                   | 0.19            | [0.16, 0.24] | True |

| $V_{cal}$ HIGH OFFSET                  | -2.0            | [-23, 17]    | True |

| $V_{cal}$ HIGH LINEARITY               | 0.52            | [0.0, 4.0]   | True |

| $V_{cal}$ HIGH LINEARITY SMALL RANGE   | 0.43            | -            | -    |

| $V_{cal}$ HIGH SLOPE SMALL RANGE RATIO | 0.5             | [0.49, 0.51] | True |

| $V_{cal}$ MED SLOPE SMALL RANGE RATIO  | 0.5             | [0.49, 0.51] | True |

Table 5.2.: Results of the  $V_{cal}$  calibration for FE 0x1794d (part of Q52).

measured value is compared against expectations (target:  $7.87 \pm 1.13 \,\text{fF}$ )[35]. Accurate capacitance measurement is crucial for interpreting threshold and noise in elementary charge units.

Figure 5.6.: Results of the Injection Capacitance measurement for an FE from module Q52. Overall, five measurements were taken and the average used to satisfy the QC criteria.

**Data Transmission** The data transmission test evaluates the quality and reliability of the high-speed communication links between the module and the readout system. This is done via an eye diagram measurement (further detailed in the upcoming section).

Low Power (LP) Mode The LP mode test checks the module's functionality when operated under reduced power conditions, as required during integration and wiring into the system after installation. The module is powered with the nominal LP current, and key voltages are measured. These include the analogue and digital supply voltages, offset voltages, and shunt currents. Additionally, data transmission is tested in LP mode by running an LP digital scan and confirming connectivity.

**SLDO Qualification** The Shunt Low Dropout (SLDO) regulator qualification tests the internal voltage regulation mechanism of each front-end chip. The module is powered with a range of input currents, and the input voltages, supply voltages, and shunt currents are recorded. This test ensures stable and predictable voltage regulation across the module's operating range.

#### 5.2.2. YARR Scans

A YARR (further detailed in section 6.2.2) scan is defined via a descriptive JSON file containing data-taking and plotting logic. The procedure consists of nested loop operations for injecting charges into the analogue or digital parts of the detector while applying varying pixel masks. Three key scan routines are part of the QC process: the Minimum Health Test (MHT), the Tuning Test (TUN), and the Pixel Failure Analysis (PFA). These stages, as visualised in Figure 5.2, test the module's health, tuning parameters, and pixel-wise performance.

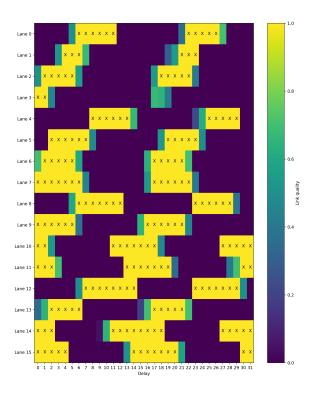

#### Eye Diagram

The eye diagram is a digital diagnostic tool used to assess the signal quality of high-speed serial data links. By overlaying multiple signal cycles, a characteristic 'eye'-shaped plot is formed.

In YARR, the eye diagram evaluates communication between the RD53B chip and the read-out FPGA (Field Programmable Gate Array) (e.g., KC705) over Aurora links. These links operate at gigabit speeds, requiring precise timing. The de-serializer delay is systematically scanned, and for each delay setting, the number of received non-idle frames is counted. Comparing this to the expected frame count yields a link quality metric:

$$S_{\text{Quality}} = \frac{\log \frac{N_{\text{expected}}}{|N_{\text{measured}} - N_{\text{expected}}|}}{13}$$

(5.1)

For perfect signal integrity ( $N_{\text{measured}} = N_{\text{expected}}$ ), the expression diverges towards infinity. To keep the metric bounded and easy to interpret,  $S_{\text{Quality}}$  is capped at 1, which represents

#### 5. Module Quality Control (QC)

a perfect or near-perfect link quality.

Figure 5.7.: Visualisation of the YARR-based eye diagram. For each link lane (y-axis), the link quality is shown for different delay settings.

For every link, the centre of the widest continuous region with perfect link quality is chosen as the optimum delay setting to be stored in the controler configuration file and later applied to subsequent scans. Due to the strong dependence of the signal quality on the exact hardware connection, it is sensible to rerun an eye diagram after every change of cables, adapters, or similar. Failing links may indicate hardware issues, primarily connection losses, as well as a misconfigured link speed or generally poor signal quality.

#### Digital Scan

Digital scans test the logic functionality of the front-end chip, including address decoding, command handling, and signal routing. Failing pixels in these scans may indicate faulty or misconfigured pixels, communication issues, or logic faults.

#### Analogue Scan

This scan verifies the analogue signal chain-amplification, discrimination, and signal uniformity across the pixel matrix. Results are used to identify noisy or non-responsive pixels. Known charges are repeatedly injected into the pixel matrix and resulting hits

are registered. The number of hits for a given pixel must closely match the number of injected charges.

#### Threshold Scan

The threshold of a given pixel is the minimum amount of charge required to register as a hit in the onboard electronics (discriminator). The duration that this threshold is surpassed is the time over threshold (ToT) and is directly proportional to the induced charge. The threshold scan is used to calibrate this value for every pixel using the internal calibration circuitry to inject known charge amounts while measuring the pixel response. This procedure can detect noisy and entirely dead pixels. In operation, the threshold value helps suppress undesired signals caused by noise, leakage currents or a number of other external influences on the sensor, in an effort to isolate the desired signal of a given interaction.

#### Merged & Discontinued Bump Scan

The merged and discontinued bump scan is used to assess the physical bump-bond connectivity between the actual sensor and its readout chip. In a properly assembled module, each bump pad connects a sensor pixel to its corresponding front-end electronics channel. However, defects during the flip-chip bonding process can lead to merged bumps (where two or more pixels are shorted together) or discontinued bumps (where a pixel is disconnected and does not respond to signals).

This scan injects charge in patterns designed to isolate and detect such anomalies. By analysing hit maps and comparing the activated pixels to the expected geometry, merged or missing connections can be identified.

#### Tuning Scans

Tuning scans aim to calibrate the analogue and digital front-end parameters on a perpixel basis to achieve uniform detector performance. Parameters such as threshold, time over threshold (ToT) response, injection capacitor gain, and feedback current are subject to local variations due to production tolerances. These variations, if left uncorrected, can lead to inconsistent signal detection and affect overall detector resolution and noise performance.

The tuning procedure involves multiple iterations of threshold and ToT scans, during which configuration parameters (such as DAC settings for thresholds and feedback) are adjusted. The goal is to equalise the detector response across all pixels, setting the

#### 5. Module Quality Control (QC)

threshold to a target value and calibrating the ToT to correspond to specific charge values. Well-tuned modules display narrow threshold and ToT distributions and minimal spread in pixel performance. Tuning is a critical step in module qualification ensuring uniformity.

## 6. Test Setup

#### 6.1. Hardware

To conduct the tests mentioned earlier (see section 5.2.1 and 5.2.2), specialised equipment and a comprehensive testing setup are required.

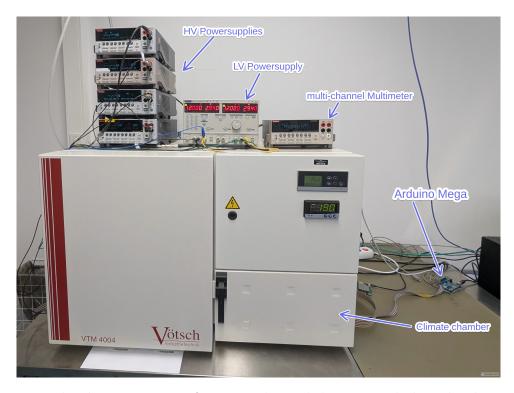

Figure 6.1.: Utilised testing setup after upgrades and changes, including the climate chamber (bottom), the Keithley 2410 HV power supplies (leftmost stack on top), the LV PS (centre top), and the multimeter (right top) along with the Arduino Mega (on the far-right side of the table).

An overview of the entire test setup is presented in Figure 6.1. For electrical QC, each quad module connects to a power and a data adapter PCB through two flex cables (further visible in Figure 6.3 front and rear of the mounting plate). These PCBs link the module to the PCIe card (via a DisplayPort cable) for data acquisition, an Arduino (for temperature monitoring), a multimeter (for onboard electrical checks), and low voltage/high voltage

(LV/HV) supplies (providing the power for operation and bias voltage).

The modules reside within the climate chamber for cooling, which helps to prevent thermal stress and potential failures. To avoid condensation, the chamber is continuously flushed with dry air. A network of software interlocks continuously monitors the system to prevent common failure modes, including overheating and the risk of condensation.

#### 6.1.1. Climate Chamber

The testing setup employed throughout this thesis revolves around a climate chamber (Vötsch VTM 4004), within which, initially, up to two, and now up to four quad modules can be placed. It is based on an earlier configuration established in the works of Niklas Grün [36] and Yusong Tian [37], which provide more detailed descriptions of certain aspects of the infrastructure. In this configuration, the modules are cooled by the surrounding air, with the climate chamber facilitating the cooling of the air itself to maintain a stable temperature environment. To ensure a homogenous temperature, a fan is used to circulate the air within the chamber. However, an alternative approach is utilised in the new testing box, where direct cooling of the modules is achieved using Peltier elements. This method allows for more efficient and localised cooling, thereby enhancing the thermal management of the modules during testing and improving overall performance.

Each module is connected to the readout PC's FPGA card via a DisplayPort cable through a corresponding data adapter PCB. Additionally, the modules are connected to a power adapter PCB that interfaces with an LV power supply, delivering 5.89 A at a maximum voltage of 3 V per quad module, alongside an HV power supply capable of delivering up to 200 V. While the former is responsible for supplying operational power to the quad module, the latter is required to set the bias voltage of the sensor.

Initially, the setup required two separate LV power supplies to handle two individual quad modules, thereby providing an independent power supply for each quad module. However, the current configuration allows all four quad modules to be wired in a serial chain powered by a single supply. This modification reduces hardware setup complexity and minimises cabling while also testing the efficacy of the serial powering feature.

#### 6.1.2. Sensors & Labremote

The onboard chip temperature of each quad module is monitored from a passthrough connection of an on-chip thermal sensor. This sensor is linked on the power adapter board to an Arduino Mega. The thermal data from the modules NTCs, along with readings from an independent PT1000 temperature sensor and I2C-based SHT85 temperature and

humidity sensor within the climate chamber, are written via the Arduino Mega to a local PC through a USB serial connection. From there, the data is parsed and uploaded through Labremote to a centralised InfluxDB, enabling close to real-time monitoring (typically with a delay of less than 2 s).

Additionally, environmental data from the room, such as temperature and particulate matter counts of various sizes, are measured and recorded in the same database. The voltage and current from connected power supplies (LV and HV) are also logged into the local InfluxDB through the connected GPIB interface.

#### 6.1.3. Database and Grafana

The overall system status is visualised through a series of Grafana dashboards that display temperatures, humidity levels, voltages, and other custom fields as time-series plots and gauges (see Figure 6.2). This visualisation aims to provide an intuitive overview of the system's status and is a crucial tool when running and monitoring electrical QC scans.

Figure 6.2.: Grafana dashboard to monitor environmental factors including relative humidity and temperatures. Further dashboards include those to monitor power and progress/status.

An active notification system is established to proactively alert users in case the system reaches a critical state, such as a module approaching unsafe temperatures or at risk of condensation due to a higher dew point. These warning messages are sent by Grafana to a designated Slack group, allowing for a prompt and efficient response to maintain system integrity and avoid compromising the functionality of the modules.

Upon completion of a test or scan, the results can be uploaded to a 'localdb' for storage and approval, after which it will be passed on to the production database. Within the

#### 6. Test Setup

localdb, all modules, their components, original location on the production wafer, as well as a historic record of all scans and tests run on any particular module can be viewed.

#### 6.1.4. Interlock Systems

In order to prevent damage to a module or the occurrence of unsafe testing conditions, continually running software interlocks are employed. Each quad module is monitored by a dedicated interlock process that tracks its onboard temperature and dew point, calculated from the thermal data stored in the central database instance.

If an interlock condition is triggered due to overheating or a risk of condensation, the system swiftly enters a safe state.

An interlock process routinely checks that the monitored parameters remain within limits defined in a configuration file. These limits include:

#### • Temperature thresholds:

- Absolute upper bounds for module temperature (40°C)

- Minimum  $\Delta T$  between the module and the environment (dew point margin) (2 °C and 5 °C for error state and warning, respectively)

#### • Current thresholds:

- Maximum allowed bias current

- Maximum acceptable current variation and fluctuation

#### • Timeouts:

- Maximum allowed age of the latest sensor reading

- Warning and critical thresholds for data freshness (20s and 40s, respectively)

When an interlock condition is triggered, the corresponding power supplies are ramped down and subsequently switched off. A file lock is also released to signal to other software components that an interlock is active. In cases of dew point-triggered interlocks, the chamber is brought to a safe state by raising its internal temperature to 25 °C.

## 6.1.5. Mounting Plate

To facilitate testing of four quad modules within the climate chamber, a custom 3D-printed mounting plate was designed and fabricated by the author in the course of this

thesis. This upgrade was essential for organising the modules, adapter PCBs, and cabling within the limited space of the climate chamber.

Throughout this thesis, frequent thermal issues were observed in pre-production modules, which often exhibited suboptimal thermal behaviour. Some modules overheated even when operating near the minimum temperature of  $-35\,^{\circ}$ C, highlighting the necessity for robust cooling and monitoring strategies. The mounting plate was designed with perforations on every flat surface to enable better movement of air, the coolant, around the modules while still remaining rigid enough to withstand daily wear and tear. Unlike the previous dual module setup in the climate chamber, in which modules were simply laid flat onto the rack without any fixation, the mounting plate provides mounting pins on which a module can be placed. This prevents the modules from moving around and subsequently knocking loose any cables during operation, as well as raising a module to allow for more air circulation directly below the metal carrier, the main heatsink.

The part was manufactured using a common fused filament fabrication 3D printer with PLA (polylactic acid) plastic and a layer height of 0.2, mm and 20% gyroid infill. The design was optimised for mechanical stability and airflow while ensuring compatibility with the existing infrastructure inside the climate chamber.

Figure 6.3.: Inside of the climate chamber. Quad modules are inserted onto the visible pins on the mounting plate and connected via the flex cables to the front and rear adapter PCBs. Cables are passed through the hole in the climate chamber on the left.

**New QC Box** To accommodate the projected QC workload, a new and streamlined testing configuration is currently being built and finalised in parallel with this thesis project. The newly assembled QC Box is designed to test up to four modules simultaneously, and it is functionally similar to the setup utilised during the course of this thesis

#### 6. Test Setup

while also improving upon it [38]. The experiences gained from the climate chamber setup, particularly in the area of parallelising various scans, will be directly transferable to the new testing box, playing a crucial role in optimising the QC procedure and assuring adequate throughput.

#### 6.2. Software

Control over the hardware components is distributed among several software systems, including Labremote, YARR, and ModuleQCTools. While the former provides monitoring data as previously mentioned through interfacing with an Arduino Mega, the latter two are for data readout and module measurements and are thus crucial for the electrical QC.

#### 6.2.1. Module QC Tools

The module-qc-tools repository is a Python-based suite of scripts and tools for running QC measurements on ITkPixV1.1 and ITkPixV2 modules. Supported tests include: ADC calibration, analogue readback, data transmission, injection capacitance, IV measurement, low power mode, SLDO qualification, and  $V_{cal}$  calibration as specified in section 5.2.1. The measurements are generalised and controled by single scripts, with the hardware and control methods specified in a central configuration file.

#### 6.2.2. YARR

The Yet Another Rapid Readout (YARR) software framework is a readout system developed for the configuration, control, and data acquisition of hybrid pixel detector modules.

YARR provides a flexible and extensible environment for interacting with front-end electronics, particularly the RD53 family of chips, including the RD53A, RD53B, and RD53C chipsets, used in ITk pixel modules. Its core functionalities include:

- Chip and module configuration: Through JSON-based configuration files, YARR enables detailed control of chip-level parameters, global registers, and module-level settings.

- Scan and test automation: YARR supports a wide variety of scan types, such as threshold scans, noise scans, and digital tests, which are essential for characterising detector performance during module production and qualification.

- Data acquisition (DAQ): The framework interfaces with FPGA-based hardware platforms (e.g., Xilinx KC705, VCU118) to manage real-time readout of pixel data and buffering of event information.

- Parallelisation and scalability: YARR can be configured to operate multiple modules simultaneously, an essential feature for scaling QC operations to production levels. This feature is to be put to the test.

YARR is written in C++ with Python bindings and uses descriptive JSON files to define scan logic and hardware configurations. It is co-developed by the ATLAS ITk community and is designed to adapt to evolving detector and hardware requirements.

The YARR Firmware is flashed onto the DAQ PC's Xilinx KC705 FPGA card using Vivado Lab software, while the YARR software package manages and coordinates scanning and testing procedures as detailed in section 5.2.2.

The goal of this thesis is to evaluate the feasibility and viability of parallelising electrical quality control tests for silicon pixel detector modules. As most tests are executed using the YARR software framework, a central focus is placed on assessing the degree to which YARR-based scans can be parallelised. In total, six quad modules were available for testing during this thesis: Q28, Q29, Q49, Q51, Q52, and Q55. An additional seventh module, Q17, was used exclusively for the final scan series Module Q28 was found to be faulty from the beginning and could not establish a functional link during eye diagram scans. As such, it was excluded from all subsequent tests.

To quantify the degree of parallelisation, we define the parallelisation percentage p as the normalised duration of a parallel run:

$$p = \frac{T_n}{T_1} \cdot \frac{1}{n} \tag{7.1}$$

Here,  $T_1$  is the scan duration for a single module, and  $T_n$  is the total duration when testing n modules in parallel.

The uncertainties here are given through Gaussian error propagation with the standard deviation of a set of time measurements as the error:

$$\sigma_P = \frac{1}{n} \sqrt{\left(\frac{\sigma_{T_n}}{T_1}\right)^2 + \left(\frac{\sigma_{T_1} \cdot T_n}{T_1^2}\right)^2} \tag{7.2}$$

## 7.1. Electrical Characterisation

The electrical characterisation tests rely on an external multimeter to measure basic electrical properties such as current draw, voltage stability, and power-up behaviour. As

<sup>&</sup>lt;sup>1</sup>The QXX identifiers are only abbreviated codenames for the longer, more descriptive identifiers. These are 20UPGM22101121, 20UPGM22101122, 20UPGM22110565, 20UPGM22110470, 20UPGM22110471, 20UPGM22110518, and 20UPGM22110467, respectively.

these instruments are available on a per-module basis, a high degree of parallelisation can be expected.

#### 7.1.1. IV Measurement

The IV (current-voltage) measurement only requires control over each module's high-voltage (HV) power supply. As each test slot is equipped with its own HV supply, a high degree of parallelisation is possible. Modules Q49, Q51, Q52, and Q55 were installed in slots 1 through 4, respectively, with the climate chamber set to 15 °C.

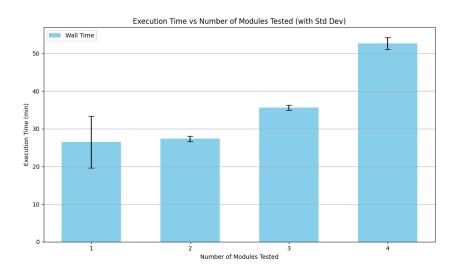

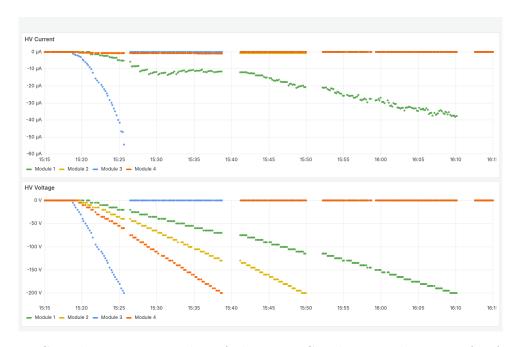

Measurements were launched in parallel using Python's multithreading library to run the module-qc-tools IV measurement script. For each test run, a random subset of the installed modules was selected, and each corresponding IV scan was executed in a separate thread. The time from the start of the first thread to the end of the execution of the last thread was recorded for each test run. Each configuration was tested in six independent repetitions. The resulting duration times versus the number of active modules are shown in Figure 7.1, with the error assumed to be of a statistical nature, derived from the standard deviation across all respective repetitions. A sample time series of a single test run with all four quad modules enabled, as displayed in Grafana, is shown in Figure 7.2.

Figure 7.1.: Total execution times for running the IV measurement on one, two, three, and four quad modules simultaneously using the varying HV power supply. No linear fit is shown, as the data exhibits clear deviations from linear behavior and the reduced chi-squared value of a potential linear regression ( $\chi^2_{\rm red} \approx 38$ ) indicates a poor fit quality.

As can clearly be observed in Figure 7.2, there are significant timing inconsistencies between different slots tested. This was traced back to the different models of HV power

Figure 7.2.: Sample time series plot of the HV PS voltage and current for four quad modules running one IV measurement using different HV PS. Slots where no data is recorded correspond to a PS being in ramp down mode, blocking all other command executions.

supplies utilised (Modules 1, 2, and 4 are connected to SHQ 122M supplies while Module 3 is connected to a Keithley 2410). Additionally, it can be observed that during the ramp-down period after the maximum bias voltage is reached, the HV PS blocks all other processes (including data taking) running simultaneously until fully ramped down. While the SHQ 122M supplies take  $\approx 2.3$  min each, the Keithley 2410 has a ramp-down period of  $\approx 0.7$  min.

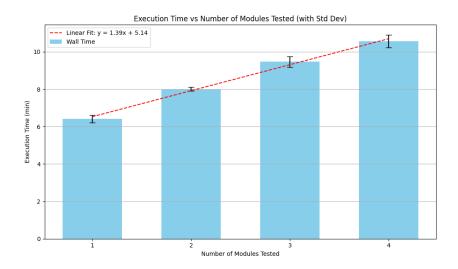

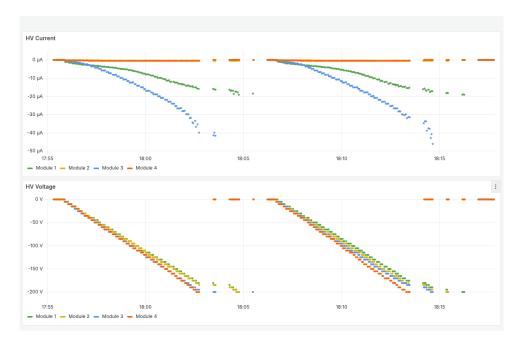

The benchmarking procedure was repeated after modifying the setup to use four identical Keithley 2410 HV PS units, replacing the heterogeneous set of supplies used previously. The resulting test durations versus the number of modules are displayed in Figure 7.3, along with a time series overview of two test cycles using the uniform HV PS in Figure 7.4.

This switch to uniform HV PS shows a clear improvement in timing reproducibility across the different slots, as well as an overall reduction in testing time. A linear fit across these timings can be applied to get an approximation for the scan duration depending on the number of modules scanned, as given in Figure 7.3.

The new Keithley 2410 HV PS units achieve the set voltage increments faster and require shorter times to settle on the desired voltage level, leading to an overall reduction of the single-module test time from as long as  $\approx 55 \,\mathrm{min}$  with the old setup down to merely  $\approx 6 \,\mathrm{min}$  using the new HV PS for a single quad module. The degree of parallelisation

Figure 7.3.: Total execution times for running the IV measurement on one, two, three and four quad modules simoultaneously with identical Keithley 2410 HV PS. The fit is given as  $y = (1.39 \pm 0.08)x + (5.14 \pm 0.08)$  with  $\chi^2_{red} = 0.74$ , indicating a good fit.

achieved with the upgraded setup for 2, 3, and 4 modules, respectively, is shown in Table 7.1. The error is given through a Gaussian error propagation:

| # Modules | Degree of Parallelisation |

|-----------|---------------------------|

| 2         | $(62.4 \pm 2.2) \%$       |

| 3         | $(49.2 \pm 2.2) \%$       |

| 4         | $(41.2 \pm 1.9) \%$       |

Table 7.1.: Measured parallelisation percentage for IV scans using 2-4 modules.

## 7.1.2. Further Electrical QC Tests

Parallelising the further electrical QC tests, including ADC calibration, analogue read-back, VCAL calibration, injection capacitance, data transmission, LP-mode, and SLDO yielded no usable results, as any parallelised scans exited immediately, leaving only one test running at a time. Across all remaining electrical QC tests, a common error scheme was observed, with the respective scans terminating when attempting to initialise a YARR instance. As no successful parallelised scan runs were feasible, no further data could be gathered and analysed.

Figure 7.4.: Sample time series plot of the HV PS voltage and current for four connected quad modules running two IV measurements back to back using the Keithley 2410 PS. The durations lacking datapoints are those during wich a PS was in a ramp-down phase, thus blocking further command execution on the GPIB interface and halting all other running processes.

# 7.2. YARR-Based Functional Scans

This section systematically evaluates the parallelisability of the YARR-based functionality scans. All distinct scan types from the MHT, TUN, and PFA testing stages were considered and compared in a structured manner to assess their suitability for parallel execution. This evaluation forms a crucial basis for understanding potential bottlenecks and opportunities for optimisation in the upcoming quality control campaign. As opposed to the previously mentioned electrical characteristic tests, a test here does not require the careful synchronisation of multiple tools. Those tests typically involve coordinating several components, including a YARR instance, which prevents multiprocessing. In contrast, a single YARR instance can be called with multiple quad modules passed as arguments. This enables the processing of multiple modules at once and avoids the need to spawn multiple YARR instances.

#### 7.2.1. Initial Tests and Software Verification

To validate the hardware setup and to gain familiarity with the test procedures, initial test scans were conducted on all available modules using the proven single-module con-

figuration. Modules Q29 and Q51 showed irregular scan behaviour, with error rates of approximately 4 out of the first 14 scans<sup>2</sup>. A selection of some of these scan results is presented in Section 5.2.2.

Subsequently, all core software components-including YARR, module-qc-tools, and supporting utilities-were upgraded to their latest stable versions, as recommended during a module QC coordination meeting. In parallel with the firmware upgrade, the link bandwidth was increased from 640 Mbps to 1280 Mbps in order to test the high speed data link at the speed required during operation.

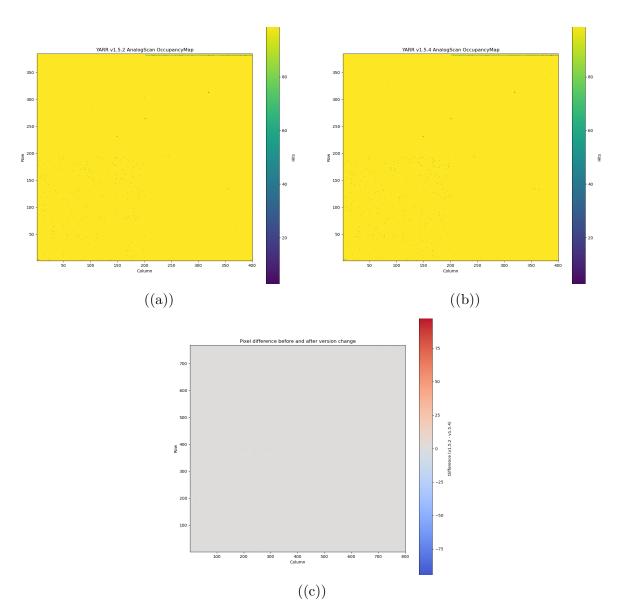

To verify that the software and firmware upgrades did not introduce inconsistencies, comparative scans (limited to digital and analogue scans) were performed on identical modules before and after the upgrade. A pixel-wise difference between pre- and post-upgrade scan results was computed to confirm stable behaviour; ideally, the resulting difference map should be uniform. An illustrative example for module Q49 is shown in Figure 7.5. Overall, the scan outputs appear nearly identical, confirming the correct functionality of YARR version 1.5.4.

#### 7.2.2. Scan Runtime

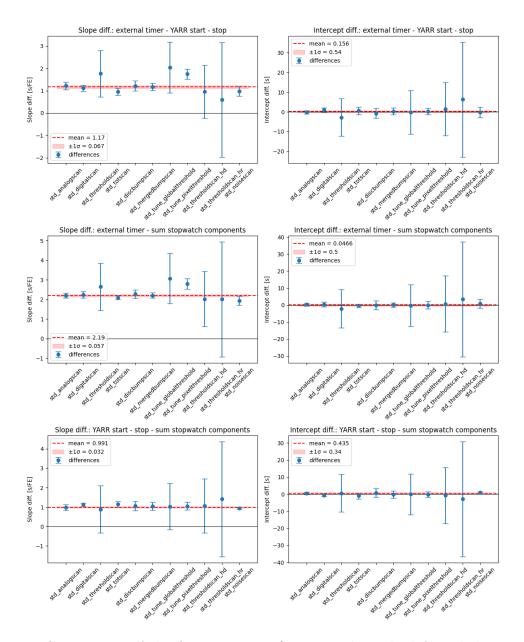

A central aspect of this thesis is the duration of a given scanning procedure. Throughout the initial investigations and preliminary tests, it became evident that the runtime of these scans can be measured and quantified in three distinct ways:

- YARR log timing: YARR records start and end timestamps within the scanLog.json file. The difference between these timestamps defines the total scan duration.

- Stage timing: Embedded stopwatch timers during scan execution, also stored in scanLog.json, yield individual durations for each scan stage (configuration, scan, analysis, and processing). These values provide insights into the duration of each component, and their sum yields the total scan time, but not the same value as the aforementioned.

- External timing: Measurement of total elapsed time via an external system timer for measuring the actual command execution time (e.g. implemented in Python).

These methods consistently report differing values for the same scan. External timing typically yields the longest duration, followed by the difference between start-end time-stamps, while the sum of individual stage durations is consistently the shortest. For most

<sup>&</sup>lt;sup>2</sup>Scan errors refer to failures reported by YARR, typically caused by poor signal integrity, faulty FE chips, or unstable configuration.

Figure 7.5.: Analogue scan occupancy map of module Q49 running YARR version 1.5.2 (top left), version 1.5.4 (top right), and the pixel-wise difference (bottom).

scans discussed in this thesis, all three timing methods were recorded. Unless otherwise noted, all subsequent scan timing analyses are based on the internal stopwatch timing to provide the most granular and consistent picture of scan execution times.

#### 7.2.3. Front-End-Wise Scan Times

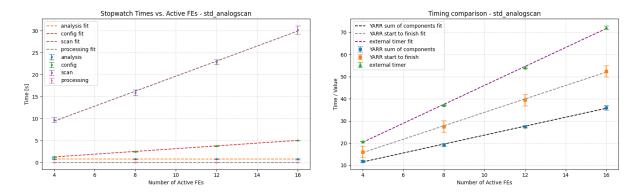

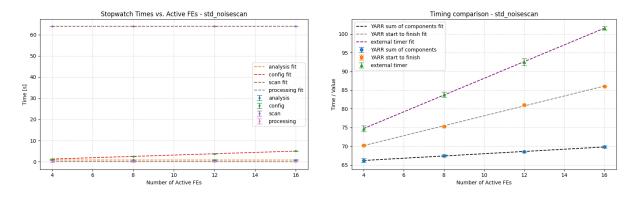

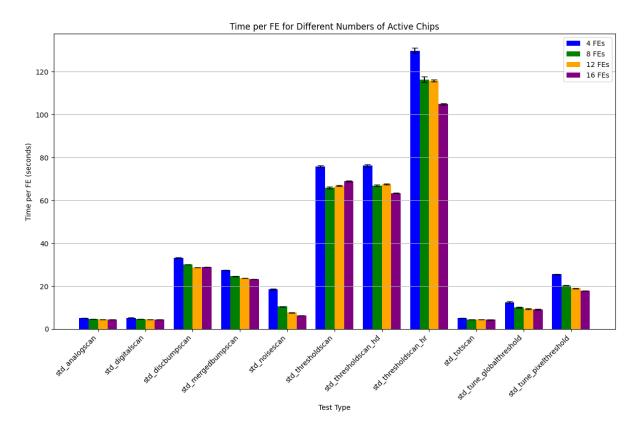

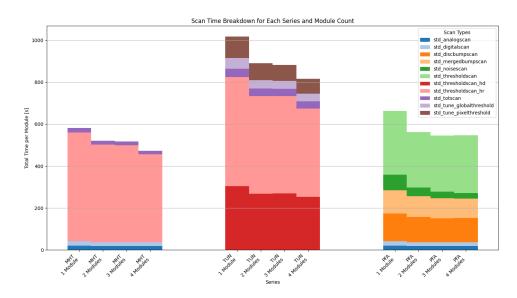

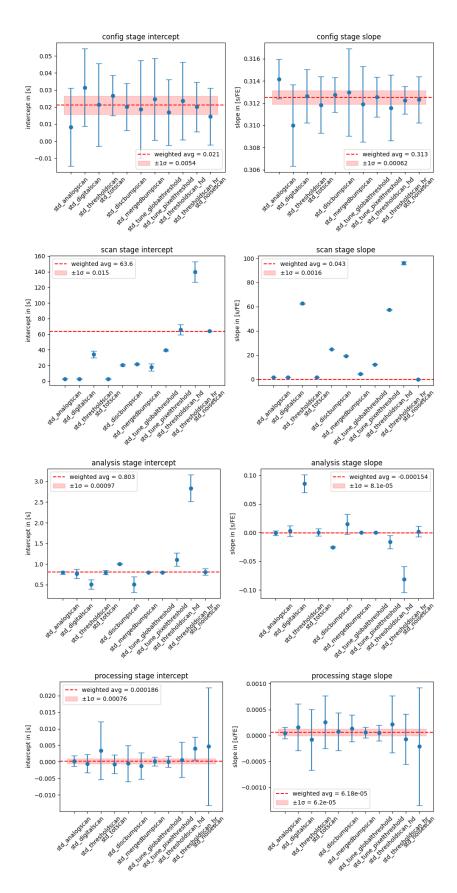

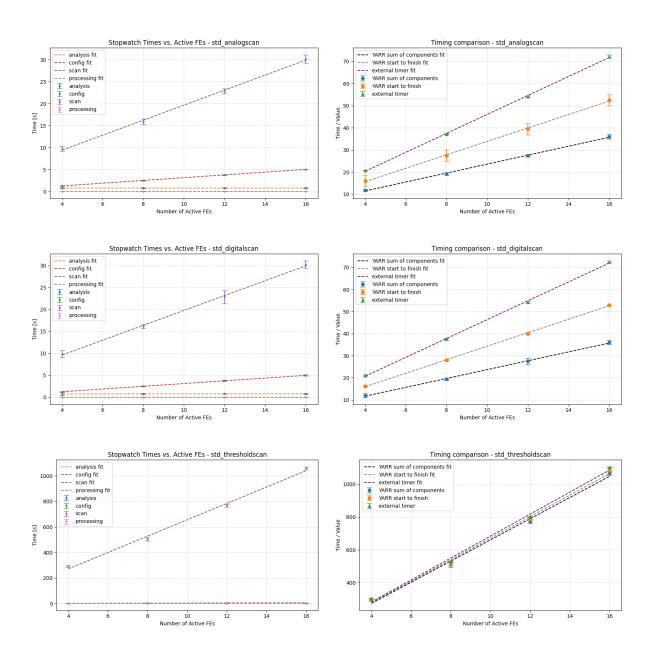

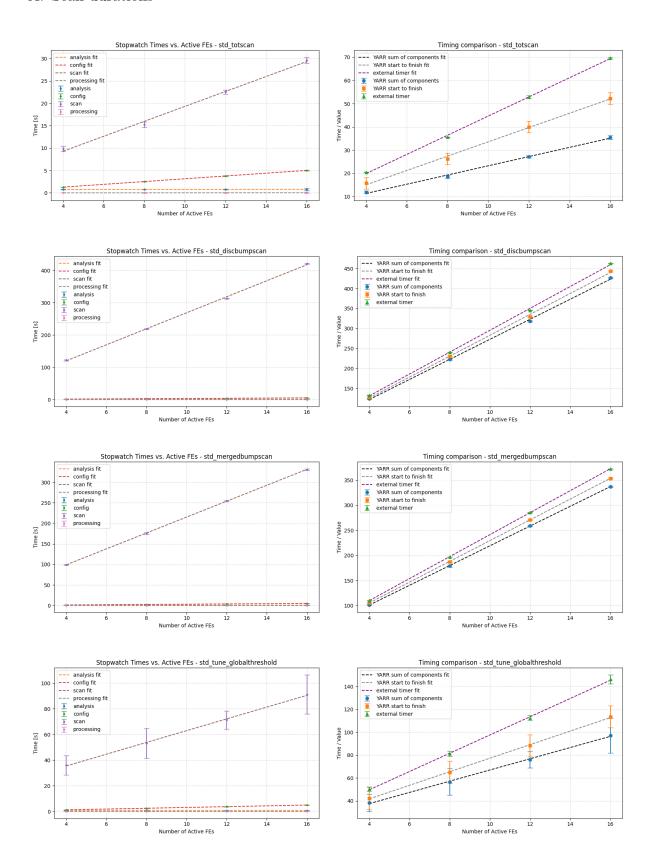

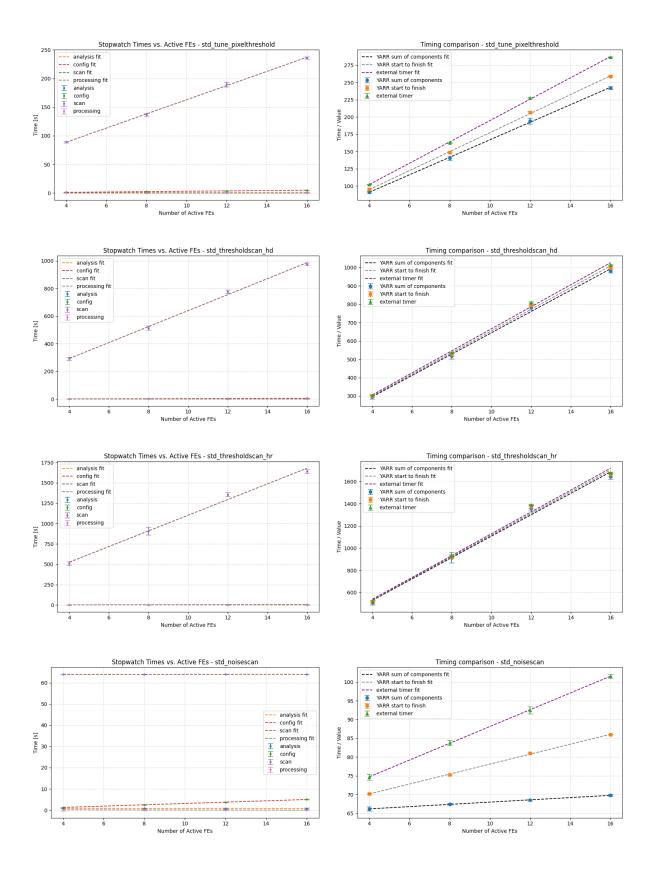

To assess the degree of parallelisation across different YARR scan types, dedicated tests were performed with 1, 2, 3, and 4 quad modules operated simultaneously. Modules Q17, Q49, Q51, and Q55 were placed in slots 1, 2, 3, and 4, respectively. These tests systematically varied the number of active front-end (FE) chips per module, evaluating configurations with 4, 8, 12, and 16 FEs. For each FE configuration, six random subsets out of the total 16 FEs were selected and activated via their corresponding configuration files. For every subset, all scan types were executed consecutively, and the command execution time was independently recorded for each scan and later re-associated with the corresponding run. The average duration of each scan stage-configuration, scan, analysis, and processing, as a function of the number of enabled front-end chips (FEs) can be evaluated individually for every scan type. For each scan stage, a linear relationship of the form

$$T = a \cdot n + b \tag{7.3}$$

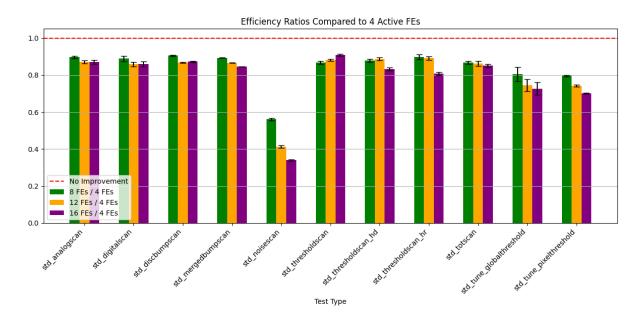

is fitted, where T denotes the time duration, n the number of active FEs, and the fit parameters a and b represent the runtime per module and the constant overhead, respectively.